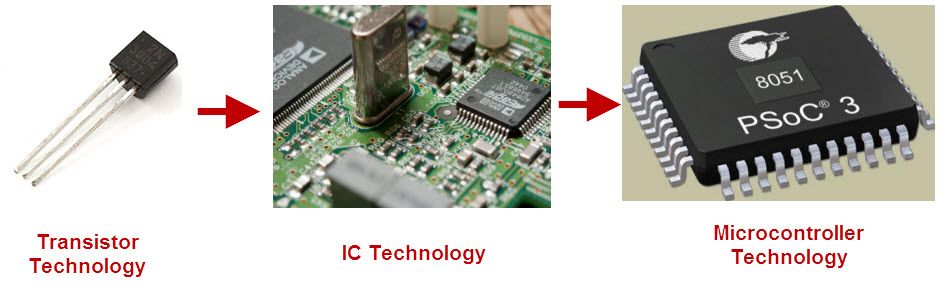

Termenul VLSI înseamnă „Tehnologie de integrare la scară foarte mare” care implică proiectarea de circuite integrate (IC-uri) prin combinarea a mii de tranzistoare logic într-un singur cip de diferite circuite logice . Aceste circuite integrate reduc în cele din urmă spațiul ocupat al circuitului în comparație cu circuitele cu circuite integrate convenționale. Puterea de calcul și utilizarea spațiului sunt principalele provocări ale designului VLSI. Implementarea proiectelor VLSI deschide o carieră provocatoare și strălucitoare atât pentru studenți, cât și pentru cercetători. Unele dintre noile zone de trend ale VLSI sunt Matrice de poartă programabilă pe câmp aplicații (FPGA), design-uri ASIC și SOC-uri. O listă cu unele dintre proiectele VLSI este prezentată mai jos pentru acei studenți care caută cu seriozitate proiecte în acest domeniu. Acest articol discută o prezentare generală a proiectelor VLSI bazate pe FPGA, Xilinx, IEEE, Mini, Matlab etc. sunt enumerate mai jos. Aceste proiecte sunt foarte utile pentru studenții ingineri, studenții M.tech.

Proiecte VLSI pentru studenți ingineri

Proiectele VLSI cu rezumate pentru studenții ingineri electronici sunt discutate mai jos.

Proiecte VLSI

1). Transformarea undelor discrete pe bază de ridicare 3D

Acest proiect ajută la furnizarea de imagini extrem de precise prin utilizarea codării unei imagini fără a-și pierde datele. Pentru a atinge acest lucru, acest proces implementează un filtru de ridicare în funcție de transformarea arhitecturii VLSI cu undă discretă 3D.

2). Proiectarea multiplicatorului SFQ cu 4 biți cu hardware eficient de mare viteză

Acest proiect este utilizat în principal pentru implementarea unui codificator de stand modificat (MBE) cu SFQ pe 4 biți multiplicator . Acest multiplicator oferă performanțe bune în comparație cu codificatorul convențional de stand. Acest proiect este utilizat în principal în aplicațiile de întârziere critică.

3). Procesor de criptografie utilizat în cardurile inteligente cu o zonă eficientă

Acest proiect este utilizat pentru a implementa trei algoritmi de criptografie suportați atât de cheile private, cât și de cele publice utilizate în card destept aplicații pentru furnizarea de date și verificări extrem de securizate ale utilizatorilor comunicare .

4). Un multiplicator de mare viteză sau de putere redusă cu metodă de suprimare a spuriei de putere

Acest sistem propus filtrează semnalele inutile false ale unităților aritmetice pentru a evita transmiterea datelor inutile care nu influențează ultimele rezultate de calcul. Acest sistem folosește o metodă SPST pentru multiplicatori pentru a realiza o transmisie de date cu putere redusă și viteză mare.

5). Compresia și decompresia unui algoritm de date fără pierderi

Acest proiect este implementat în principal pentru arhitectura hardware în două etape, în funcție de caracteristica algoritmului PDLZW (Parallel Dictionary LZW), precum și de algoritmul de tip Adaptive Huffman care este utilizat atât pentru aplicațiile de compresie a datelor fără pierderi, cât și pentru decompresia fără pierderi.

6). Arhitectura decodificatorului turbo cu complexitate redusă pentru WSN-uri eficiente din punct de vedere energetic

Sistemul propus este utilizat pentru a reduce consumul total de energie pe parcursul transmiterii datelor WSN-urilor prin algoritmul de descompunere al LUT-Log-BCJR la operațiile de bază ACS (Add Compare Select).

7). Arhitectura VLSI pentru eliminarea eficientă a zgomotului de impuls al unei imagini

Acest sistem propus a fost utilizat în principal pentru a îmbunătăți vizual calitatea imaginii pentru a evita șansele de a fi corupt cu zgomot de impuls pentru a implementa o arhitectură VLSI eficientă cu ajutorul unui filtru de conservare a marginilor.

8). Arhitectura unui procesor de memorie utilizat pentru compresia multimedia

Acest sistem propus oferă o arhitectură de complexitate redusă pentru un procesor în memorie pentru a sprijini aplicații multimedia și anume compresia imaginii, video prin aplicarea unei instrucțiuni enorme, concepte multiple de date și cuvânt de instrucțiuni.

9). Tehnică de sincronizare sincronizată cu o rată de simbol pentru sistemele OFDM fără fir cu putere redusă

Acest sistem propus este utilizat în principal pentru a îmbunătăți actul OFDM fără fir (Divizia de frecvență ortogonală) Multiplexare ) prin scăderea puterii întregii benzi de bază cu ajutorul unui ceas generator cu regulator de sincronizare a eșantionului reglabil și dinamic.

10). Implementarea multiplicatorului cu putere redusă și viteză bazată pe acumulator cu SPST Adder și Verilog

Acest proiect este utilizat pentru a proiecta un MAC de mică putere și viteză mare (multiplicator și acumulator) prin acceptarea metodei de suprimare falsă a puterii pe un MBE (codificator de cabină modificat). Prin utilizarea acestui design, disiparea puterii pentru întreaga comutare poate fi evitată.

11). Proiectare și implementare procesor robot prin activarea anti-coliziunii cu tehnologia RFID

Sistemul propus este utilizat în principal pentru a implementa un procesor robot cu anti-coliziune pentru a evita coliziunea fizică a roboților în mediul multi-robot. Acest algoritm este implementat în principal folosind tehnologia VHDL și RFID.

12). Proiectarea circuitului logic cu eficiență energetică utilizând metoda adiabatică

Acest sistem demonstrează proiectarea circuitului logic prin metoda adiabatică eficientă, comparată prin proiectarea convențională CMOS cu ajutorul circuitelor care utilizează Porți NAND și NOR . Prin utilizarea metodei adiabatice, disiparea puterii în rețea poate fi redusă, precum și reciclarea energiei stocate în condensatorul de încărcare.

3). Sistem de criptare pentru îmbunătățirea vitezei de calcul a sistemului

Principala intenție a acestui proiect este de a spori securitatea transmisiei de date pentru a îmbunătăți viteza de calcul prin implementarea algoritmului AES folosind FPGA. Deci, această simulare, precum și proiectarea matematică, pot fi efectuate cu ajutorul codului VHDL.

14). Bloc IP de AHM sau magistrală avansată de înaltă performanță

Acest proiect este utilizat în principal pentru a proiecta o arhitectură Advanced Microcontroler Bus (AMB) folosind AHBN (Advanced High-Performance Bus). Acest proiect poate fi proiectat cu cod VHDL prin implementarea blocurilor precum master & save.

15). Transmițător RF multimod bazat pe DSM cu multicanal

Acest sistem a fost utilizat în principal pentru a proiecta un arhitectură de transmisie și receptor multimod și o multicanală RF cu modulator Delta-Sigma. Acest sistem propus folosește un limbaj VHDL pentru a implementa două arhitecturi.

16). Comutatorul concentratorului knockout utilizând un mod de transfer asincron

Prin utilizarea acestui proiect, un comutator knockout bazat pe transfer asincron poate fi proiectat cu ajutorul unor instrumente precum VHS și VHDL. Acest comutator knock out poate fi utilizat în rețelele pachetelor de circuite virtuale, precum și în aplicațiile datagramei.

17). Circuite asincrone Sinteza comportamentală

Acest proiect este utilizat în principal pentru a furniza tehnica de sinteză comportamentală utilizată pentru circuitele asincrone. Ambele șabloane, cum ar fi implementările balsa și asincrone, sunt elementele principale din cadrul designului.

18). Proiectare AMBA utilizând controlerul de memorie conform AHB

Acest proiect este utilizat pentru a proiecta un MC (controler de memorie) în funcție de AMBA (Advanced Microcontroller Bus Architecture) pentru controlul memoriei de sistem folosind memoria principală, cum ar fi SRAM și ROM.

19). Implementarea Carry Tree Adder

Adderul de arbore de transport bazat pe designul VLSI este numit cel mai bun aditiv de performanță, comparativ cu aditivii binari obișnuiți. Sumatoarele care sunt implementate de acest proiect sunt copacul, piatra kogge și piatra kogge rară.

20). CORDIC Rotația bazată pe designul unghiului fix

Principalul concept al acestui sistem propus este de a transforma vectori folosind unghiuri fixe. Aceste unghiuri sunt necesare pentru jocuri, robotică, procesarea imaginii etc. Prin utilizarea acestui proiect, rotația vectorială poate fi realizată utilizând unghiuri specifice prin proiectarea CORDIC (computer digital cu rotație a coordonatelor).

21). Proiectare filtru FIR cu aritmetică distribuită a tabelului de căutare

Acest sistem propus se îmbunătățește în principal Filtru FIR performanța prin proiectarea acesteia folosind aritmetica distribuită a unui tabel de căutare tridimensional în locul multiplicatorului. Deci, acest design poate fi implementat folosind software-uri precum FPGA și Xilinx.

22). Dispozitive de blocare Push-Pull cu condiționare de mare viteză și putere redusă

Acest proiect este folosit pentru a executa zăvoare cu impulsuri eficiente din punct de vedere energetic și de înaltă performanță utilizate în principal pentru sistemele VLSI prin utilizarea unei noi topologii. Deoarece această topologie depinde în principal de o etapă finală push-pull condusă folosind două benzi de divizare printr-un generator de impuls condiționat.

23). Aritmetic Coder VLSI Architecture in SPIHT

Acest sistem propus îmbunătățește randamentul metodei de codificare aritmetică în partiționarea setului în arborele ierarhic (SPIHT) de compresie a imaginii cu arhitectura de mare viteză în funcție de FPGA.

24). Suprimarea zgomotului semnalului ECG bazat pe FPGA

Acest proiect este utilizat pentru a conține zgomotul din semnalele ECG prin intermediul a două filtre mediane cu 91 și respectiv 7 dimensiuni ale punctelor de eșantionare. Deci, acest proces poate fi atins prin implementarea Proiectare FPGA pe baza codului VHDL.

25). Procesor de redimensionare a imaginii de înaltă performanță bazat pe VLSI, cu cost redus

Acest proiect este utilizat pentru a implementa un algoritm pentru procesarea scalării imaginii bazat pe VLSI cu mai puțină memorie și performanță ridicată. Proiectarea sistemului propusă conține în principal combinarea filtrelor, metode dinamice reconfigurabile și partajarea hardware pentru a reduce costul.

26). Proiectare și implementare eficientă a arhitecturii matrice sistolice

Principalul concept al acestui proiect este de a proiecta un model hardware folosit pentru multiplicatorul sistolic array. Această matrice poate fi utilizată în principal pentru a executa multiplicarea binară cu ajutorul platformei VHDL. Proiectarea sistemului propusă poate fi implementată utilizând software-ul FPGA și Isim.

27). Proiectare și sinteză QPSK folosind codul VHDL

QPSK este una dintre principalele metode de modulare. Această metodă este utilizată în aplicațiile radio prin satelit. Această tehnică de modulare poate fi implementată prin porți logice reversibile. Proiectarea tehnicii QPSK poate fi realizată cu ajutorul codului VHDL.

28). Proiectare și implementare controler DDR SDRAM cu viteză mare

Sistemul propus este utilizat pentru a proiecta un controler DDR SDRAM pentru transferul datelor de rafală în funcție de viteza mare pentru a sincroniza aceste date între circuitele sistemului încorporat și DDR SDRAM. Prin utilizarea limbajului VHDL, codul poate fi dezvoltat.

29). Proiectare și implementare procesor RISC pe 32 de biți

Principalul concept al acestui proiect este de a implementa un 32 de biți RISC (Reduced Instruction Set Computer) cu ajutorul unui instrument precum XILINK VIRTEX4. În acest proiect, 16 seturi de instrucțiuni sunt proiectate ori de câte ori fiecare instrucțiune poate fi executată într-un singur ciclu CLK utilizând metoda în cinci faze a conductelor.

30). Implementarea podului de autobuz între AHB și OCP

Sistemul propus este utilizat pentru a proiecta o punte de autobuz între două protocoale și anume comun și standard. Protocoalele de comunicații precum AHB (Advanced High-performance Bus) și OCP (Open Core Protocol) sunt foarte populare, care sunt utilizate în aplicațiile de SoC (System On-chip) .

Idei de proiecte VLSI pentru studenții ingineri

Lista proiectelor VLSI bazate pe FPGA, MatLab, IEEE și Mini Proiecte pentru studenții ingineri este listată mai jos.

Proiecte VLSI pentru studenții M. Tech

Lista proiectelor VLSI bazate pe M. Tech Students include următoarele.

- Proiectare celulă de memorie I0T bazată pe RHBD eficientă și extrem de fiabilă utilizată în aplicații aerospațiale

- Detector de fază cu jumătate de rată pe mai multe niveluri utilizat pentru CLK și circuite de recuperare a datelor

- Comparator cu o putere redusă și viteză mare utilizate pentru aplicații precise

- Translator de nivel de tensiune închis cu un multiplexor de înaltă performanță și integrat

- Sumator ternar bazat pe CNTFET cu performanță ridicată

- Proiectare comparator de magnitudine cu putere redusă

- Proiectarea porții logice prag cu modul curent pentru analiza întârzierii

- Design de decodoare de linie mixtă-logică cu putere redusă și performanță ridicată

- Conventia Sleep Testabilitate logică

- Schimbator de nivel de tensiune pentru aplicații cu alimentare dublă, cu viteză mare și eficiență energetică

- Proiectare și analiză a comparatorului cu coadă dublă de putere mică și de joasă tensiune

- Flip-Flop Design bazat pe impulsuri declanșate cu consum redus de energie utilizând o metodă de trecere a semnalului

- Proiectare eficientă a circuitelor bazate pe FET-uri reconfigurabile Runtime

- Proiectare comparator de magnitudine cu putere redusă

- Analiza întârzierii proiectelor de poartă logice cu prag de mod curent

Proiecte VLSI bazate pe FPGA pentru studenții ingineri și Mini-proiecte de proiectare CMOS VLSI sunt enumerate mai jos.

- Proiectare și caracterizare circuite întărite SEU pentru FPGA pe baza SRAM

- O aplicație potențială LUT hibridă CMOS bazată pe Memristor compact, utilizată în FPGA

- Implementarea bazată pe senzor cu ultrasunete a FPGA pentru măsurarea distanței

- Implementarea FPGA pentru multiplicatorul de standuri cu Spartan6 FPGA

- Transformare discretă de pachete bazată pe ridicare cu Spartan3 FPGA

- Controler ARM în robotică folosind FPGA

- UART bazat pe FPGA cu multicanal

- Suprimarea zgomotului semnalului ECG utilizând FPGA

- Implementare FPGA bazată pe UTMI și strat de protocol USB 2.0

- Implementarea Filtrului Median cu Spartan3 FPGA

- Implementarea algoritmului AES bazat pe FPGA

- Sistem de alertă de securitate bazat pe PIC pentru implementarea FPGA cu Spartan 3an

- Implementare FPGA pentru proiectarea controlerului pentru sistemele de teledetecție

- Trusa de procesare a imaginilor FPGA folosind filtrarea imaginilor liniare și morfologice

- Spartan3 FPGA bazat pe implementarea imaginii medicale de fuziune

Lista de Mini proiecte VLSI folosind cod VHDL include următoarele.

- Comparator cu viteză mare utilizând VLSI

- Un multiplicator de virgulă mobilă utilizând VLSI

- Conversia bazată pe VLSI a binarului în gri

- Filtru digital

- CLK Gating bazat pe VLSI

- Multiplicator vedic

- CMOS FF folosind VLSI

- Arhitectura procesorului paralel care utilizează VLSI

- Adder complet bazat pe VLSI

- Proiectarea memoriei DRAM / Dynamic Access Random Access bazată pe VLSI

- Layout SRAM bazat pe VLSI

- Procesor de semnal digital bazat pe VLSI

- Multiplexor bazat pe VLSI

- Proiectarea unității MAC bazată pe VLSI

- Diferențiator bazat pe VLSI

- FFT bazat pe VLSI sau Transformată Fourier rapidă

- Arhitectura transformării discrete a cosinusului bazată pe VLSI

- Proiectare multiplicator pe 16 biți folosind VLSI19

- Proiectarea bazată pe VLSI a bufferului FIFO

- Accelerator de mare viteză bazat pe VLSI

Proiecte VLSI folosind MATLAB și Xilinx

Lista proiectelor VLSI bazate pe proiectele MATLAB și VLSI care utilizează Xilinx include următoarele.

- Proiectare și analiză modem CDMA cu MATLAB

- FIR Filter Design folosind VHDL pe analize bazate pe FPGA și MATLAB

- Simulare a sistemului pentru ingineria auto bazată pe ModelSim & Matlab sau Simulink

- Addere bazate pe Xilinx precum Ripple Carry & Carry Skip

- Unitate aritmetică bazată pe virgulă mobilă pe 32 de biți

- ALU bazat pe virgulă mobilă

- Procesor RISC bazat pe 32 de biți

- Capacitățile de convoluție ale codului ortogonal

- Distribuitor automat bazat pe Xilinx și Verilog

- Addere de prefixuri paralele bazate pe Xilinx cu 256 de biți

- Protocol pentru autentificarea reciprocă utilizând Xilinx

- Structura de acces cu un singur ciclu pentru testarea logicii folosind Xilinx

- USB2.0 bazat pe UTMI & Protocol Layer folosind Xilinx

- Configurarea compresiei și decompresiei datelor folosind Xilinx FPGA

- FPGA-uri bazate pe BIST & Spartan Series bazate pe Xilinx 4000

- Filtru IIR bazat pe MATLAB și VLSI

- Filtru FIR folosind MATLAB

Proiecte IEEE

lista proiectelor IEEE VLSI este listat mai jos.

- Sistem de automatizare a domiciliului fără fir bazat pe VLSI care utilizează Bluetooth

- Eliminarea zgomotului de impuls din imagine utilizând o arhitectură eficientă a VLSI

- Arhitectura unui procesor-în-memorie pentru compresie multimedia

- Monitorizarea sistemului de temperatură utilizând Cloud & IoT

- Implementarea sistemului OFDM cu IFFT și FFT

- Proiectarea și implementarea codului Hamming cu Verilog

- Recunoaștere amprentă digitală bazată pe VHDL folosind filtrul Gabor

- Funcții aritmetice Remapare cu ROM În funcție de abordările de aproximare

- Analiza performanței ridicate și a performanței cu densitate scăzută a decodificatorului de cod de verificare a parității în aplicații de consum redus

- Arhitecturi FFT cu Feedforward de Pipelined Radix-2k

- Flip-Flops Design pentru aplicații VLSI folosind tehnologia CMOS cu performanțe ridicate

- Proiectare filtru FIR cu tabel de căutare de aritmetică distribuită

- Procesor de redimensionare a imaginilor cu cost redus și îmbunătățit bazat pe VLSI

- Implementarea și proiectarea ASIC a unui codificator și decodor Turbo Advance cu 3GPP LTE

- Dispozitive de blocare Push-Pull cu putere redusă și condiționate de mare viteză

- Scanare îmbunătățită în testarea scanării cu consum redus de energie

- Aritmetic Coder VLSI Architecture pentru SPIHT

- Implementarea VHDL pentru UART

- Regulator de tensiune bazat pe VLSI cu scădere redusă

- Proiectare ADC Flash cu schemă de comparare îmbunătățită

- Design multiplicator de putere redusă cu stil de logică de întârziere constantă

- Comparator dublu coadă cu performanță ridicată și putere redusă

- Sistem de stocare Flash cu performanțe ridicate, în funcție de tamponul de scriere și memoria virtuală

- FF de putere redusă bazat pe abordarea Sleepy Stack

- Optimizarea puterii LFSR pentru BIST de putere redusă Implementat în HDL

- Proiectare și implementare automată cu Verilog HDL

- Proiectare acumulator bazată pe generația modelului de 3 greutăți cu LP-LSFR

- Decodor Reed-Solomon cu viteză mare și complexitate redusă

- Tehnică de proiectare a multiplicatorului Dadda mai rapidă

- Receptor de radio FM bazat pe demodulare digitală

- Generarea modelului de testare cu scheme BIST

- Implementarea arhitecturii VLSI cu conducte de mare viteză

- On-Chip Bus OCP Protocol Design folosind funcționalitățile autobuzului

- Detector de frecvență de fază și design de pompă de încărcare utilizat pentru bucla blocată de fază de înaltă frecvență

- Memorie cache și design de controler cache cu VHDL

- Implementarea bazată pe ASTRAN a compresoarelor Adder 3-2 și 4-2 de putere redusă

- Sistem preplătit de facturare a energiei electrice utilizând un design On-Chip

- Implementarea suprapunerii utilizând celula logică și analiza puterii sale

- Carry Look Ahead Adder cu diferite analize de performanță pe biți folosind VHDL

- Data Link Layer Design cu Wi-Fi MAC Protocoale

- Implementarea FPGA pentru protocolul de autentificare reciprocă cu aritmetică modulară

- Generarea semnalului PWM utilizând FPGA și ciclul de funcționare variabilă

Proiecte în timp real

Lista de Proiecte VLSI în timp real includ în principal mini proiecte VLSI folosind cod VHDL și proiecte software VLSI pentru studenții ECE.

- Integrarea pragmatică a cache-ului de rând SRAM în arhitectura DRAM 3-D heterogenă utilizând TSV

- Tehnică de auto-test încorporată pentru diagnosticarea defecțiunilor de întârziere în tablourile de poartă programabile pe bază de cluster

- Proiectarea ASIC a multiplicatorului complex

- O implementare VLSI low-cost pentru eliminarea eficientă a zgomotului de impuls

- Bazat pe FPGA Space Vector PWM CI de control pentru acționarea motorului cu inducție trifazată

- Implementarea VLSI a Auto Correlatorului și a algoritmului CORDIC pentru WLAN bazat pe OFDM

- Extragerea automată a drumului utilizând imagini de satelit de înaltă rezoluție

- Proiectare VHDL pentru segmentarea imaginii folosind filtrul Gabor pentru detectarea bolilor

- O arhitectură de decodare turbo cu complexitate redusă pentru rețele de senzori fără fir eficiente din punct de vedere energetic

- Îmbunătățirea capacităților de convoluție a codului ortogonal utilizând implementarea FPGA

- Proiectarea și implementarea ALU în virgulă mobilă

- Design CORDIC pentru unghi fix de rotație

- Coduri Reed-Solomon pentru produs pentru implementarea controlerului flash NAND pe cipul FPGA

- Îmbunătățirea randamentului accesului la citire SRAM statistic utilizând circuite de capacitate negativă

- Managementul energiei interfețelor de rețea MIMO pe sisteme mobile

- Proiectarea standardului de criptare a datelor pentru criptarea datelor

- Putere redusă și suprafață eficientă Carry Select Adder

- Sinteza și implementarea UART folosind coduri VHDL

- Arhitecturi îmbunătățite pentru o unitate cu punct flotant adăugat-scăzut

- Un transmițător digital pe 1 biți bazat pe FPGA care utilizează modulație Delta-Sigma cu ieșire RF pentru SDR

- Optimizarea utilizării căutării în lanț în decodificatorul BCH pentru transmisie cu rată de eroare ridicată

- Proiectare digitală a transmițătorului DS-CDMA folosind Verilog HDL și FPGA

- Proiectarea și implementarea arhitecturii matrice sistemice eficiente

- Un algoritm de învățare a dinamicii robotului bazat pe VLSI

- Un design multifuncțional multifuncțional al unității funcționale utilizând tehnica spurie de suprimare a puterii

- Proiectarea podului de autobuz între AHB și OCP

- Sinteza comportamentală a circuitelor asincrone

- Optimizarea vitezei unui decodor Viterbi modificat pe bază de FPGA

- Implementarea interfeței I2C

- Un multiplicator de mare viteză / putere redusă utilizând o tehnică avansată de suprimare a puterii spurioase

- Strângerea tensiunii de alimentare virtuale a circuitelor electrice închise pentru reducerea activă a scurgerilor și fiabilitatea oxidului de poartă

- Canalizator cu eficiență energetică bazat pe FPGA pentru radio definit de software

- Arhitectura VLSI și Prototiparea FPGA a unei camere digitale pentru securitatea și autentificarea imaginilor

- Îmbunătățirea funcționării robotului interior

- Proiectarea și implementarea unei rețele de permutare ON-Chip pentru multiprocesor System-On-Chip

- O metodă de sincronizare a sincronizării ratei simbolurilor pentru sistemele OFDM fără fir de consum redus

- Controler DMA (acces direct la memorie) folosind VHDL / VLSI

- FFT reconfigurabil folosind arhitectura bazată pe CORDIC pentru receptoare MIMI-OFDM

- Tehnica spurie de suprimare a puterii pentru aplicații multimedia / DSP

- Eficiența codurilor BCH în filigranul digital de imagine

- Controler SD-RAM cu viteză de date dublă

- Implementarea filtrului Gabor pentru recunoașterea amprentelor digitale utilizând Verilog HDL

- Proiectarea unei scale de nanometri practice redundante prin Aware Standard Cell Library pentru îmbunătățirea redundanței prin 1 rată de inserare

- Un algoritm de compresie și decompresie a datelor fără pierderi și arhitectura sa hardware

- Un cadru pentru corectarea erorilor soft multi-biți

- Compresie eficientă a datelor de testare pe bază de Viterbi

- Implementarea blocurilor FFT / IFFT pentru OFDM

- Compresie de imagini bazată pe Wavelet prin codare progresivă VLSI

- Implementarea VLSI a multiplicatorului complet canalizat Arhitectura DCT / IDCT 2d mai mică pentru Jpeg

- Emulare de erori bazate pe FPGA a circuitelor secvențiale sincrone

Astfel, aici este vorba despre lista proiectelor VLSI pentru ingineri, studenți M.Tech, care sunt de ajutor în selectarea subiectului proiectului lor de ultimul an. După ce vă petreceți timpul prețios în timp ce parcurgeți această listă, credem că aveți o idee destul de bună de a selecta subiectul proiectului la alegerea dvs. din lista proiectelor VLSI și sperăm că aveți suficientă încredere pentru a prelua orice subiect din listă. Pentru detalii suplimentare și ajutor cu aceste proiecte, ne puteți scrie în secțiunea de comentarii de mai jos. Iată o întrebare pentru dvs., ce este VHDL?

Credit foto

- Proiecte VLSI de către set-tech