În domeniul electronicii, cel mai crucial concept la care funcționează fiecare componentă este „ Logic Gates „. Deoarece conceptul de porți logice este implementat în fiecare funcționalitate, cum ar fi în circuite integrate, senzori, scopuri de comutare, microcontrolere și procesoare, scopuri de criptare și decriptare și altele. În plus față de acestea, există aplicații largi ale Logic Gates. Există multe tipuri de porți logice, cum ar fi Adder, Subtractor, Full Sumator , Full Subtractor, Half Subtractor și mulți alții. Deci, acest articol oferă informații colective despre jumătate de circuit de scădere , tabel de adevăr pe jumătate subtractor , și concepte conexe.

Ce este Half Subtractor?

Înainte de a discuta despre jumătatea scăderii, trebuie să cunoaștem scăderea binară. În scăderea binară, procesul scăderii este similar cu scăderea aritmetică. În scăderea aritmetică se folosește sistemul numeric de bază 2, în timp ce în scăderea binară, numerele binare sunt folosite pentru scăderea. Termenii rezultați pot fi notați cu diferența și împrumutul.

Jumătate de scădere este cea mai esențială circuit logic combinațional care este folosit în electronice digitale . Practic, acesta este un dispozitiv electronic sau, cu alte cuvinte, îl putem spune ca un circuit logic. Acest circuit este utilizat pentru a efectua scăderea a două cifre binare. În articolul precedent, am discutat deja conceptele de jumătate de sumator și circuit complet de sumator care folosește numere binare pentru calcul. În mod similar, circuitul scăderii folosește numere binare (0,1) pentru scăderea. Circuitul semicontractorului poate fi construit cu două porți logice și anume porți NAND și EX-OR . Acest circuit oferă două elemente, cum ar fi diferența, precum și împrumuturile.

Ca și în scăderea binară, cifra majoră este 1, putem genera împrumut în timp ce subtrahendul 1 este superior minuendului 0 și, din acest motiv, împrumutul va avea nevoie. Următorul exemplu oferă scăderea binară a doi biți binari.

Prima cifră | A doua cifră | Diferență | Împrumuta |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

În scăderea de mai sus, cele două cifre pot fi reprezentate cu A și B. Aceste două cifre pot fi scăzute și oferă biții rezultați ca diferență și împrumut.

Când observăm primele două și patru rânduri, diferența dintre aceste rânduri, atunci diferența și împrumutul sunt similare, deoarece subtrahendul este mai mic decât minuendul. În mod similar, atunci când observăm al treilea rând, valoarea minuendului este scăzută din subtrahend. Deci, diferența și biții de împrumut sunt 1, deoarece cifra subtrahend este superioară cifrei minuend.

Acest circuit combinațional este un instrument esențial pentru orice fel de circuit digital să cunoască combinațiile posibile de intrări și ieșiri. De exemplu, dacă scăderea are două intrări, atunci rezultatele rezultate vor fi patru. O / p al jumătății scăzătorului este menționat în tabelul de mai jos, care va semnifica bitul diferenței, precum și bitul împrumutat. Explicația tabelului de adevăr al circuitului se poate face folosind porțile logice cum ar fi poarta logică EX-OR și operația de poartă AND urmată de poarta NOT.

Rezolvarea tabelului adevărului folosind Harta K este prezentat mai jos.

jumătate subtractor k hartă

expresie pe jumătate subtractor folosind tabelul de adevăr și harta K pot fi derivate ca

Diferență (D) = ( X y + X y ')

= x ⊕ y

Împrumut (B) = x’y

Circuit logic

jumătate de circuit logic subtractor poate fi explicat folosind porțile logice:

- 1 poartă XOR

- 1 NU poarta

- 1 ȘI poartă

Reprezentarea este

Circuit logic pe jumătate de subtractor

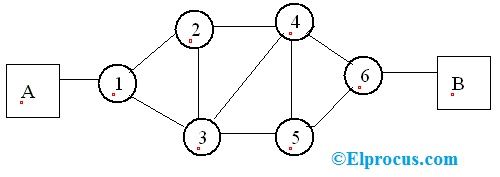

Diagrama blocului pe jumătate de subtractor

Diagrama bloc a jumătății scăderii este prezentată mai sus. Necesită două intrări, precum și două ieșiri. Aici intrările sunt reprezentate cu A&B, iar ieșirile sunt Diferență și Împrumut.

Circuitul de mai sus poate fi proiectat cu porți EX-OR & NAND. Aici, poarta NAND poate fi construită folosind porți ȘI și NU. Deci, avem nevoie de trei porți logice pentru realizarea unei jumătăți de circuite de scădere și anume poarta EX-OR, NU poarta și poarta NAND.

O combinație de poartă AND și NOT produce o poartă combinată diferită numită Poarta NAND. Ieșirea poartă Ex-OR va fi bitul Diferență, iar ieșirea NAND Gate va fi bitul Împrumut pentru aceleași intrări A&B.

ȘI-Poartă

Poarta AND este un tip de poartă logică digitală cu mai multe intrări și o singură ieșire și bazată pe combinațiile de intrări va efectua conjuncția logică. Când toate intrările acestei porți sunt mari, atunci ieșirea va fi mare, altfel ieșirea va fi scăzută. Diagrama logică a porții ȘI cu tabelul adevărului este prezentată mai jos.

ȘI Tabelul Poartă și Adevăr

NU Poarta

Poarta NOT este un tip de poartă logică digitală cu o singură intrare și pe baza intrării ieșirea va fi inversată. De exemplu, când intrarea porții NOT este mare, atunci ieșirea va fi scăzută. Diagrama logică a NOT-gate cu tabelul adevărului este prezentată mai jos. Folosind acest tip de poartă logică, putem executa porți NAND și NOR.

NU Poarta și Adevărul Tabel

Poarta Ex-SAU

Poarta Exclusive-OR sau EX-OR este un tip de poartă logică digitală cu 2 intrări și o singură ieșire. Funcționarea acestei porți logice depinde de poarta SAU. Dacă oricare dintre intrările acestei porți este mare, atunci ieșirea porții EX-OR va fi mare. Simbolul și tabelul de adevăr al EX-OR sunt prezentate mai jos.

Poarta XOR și tabelul adevărului

Circuit pe jumătate de subtractor folosind Nand Gate

Proiectarea scăderii poate fi realizată de folosind porți logice cum ar fi poarta NAND și poarta Ex-OR. Pentru a proiecta acest circuit pe jumătate substractor, trebuie să cunoaștem cele două concepte și anume diferența și împrumutul.

Circuit pe jumătate de subtractor folosind Nand Gate

Dacă monitorizăm cu precauție, este destul de clar că varietatea de operații executate de acest circuit, care este corect legată de operația de poartă EX-OR. Prin urmare, putem folosi pur și simplu poarta EX-OR pentru a face diferența. În același mod, împrumutul produs de circuitul cu jumătate de sumator poate fi atins pur și simplu prin utilizarea amestecului de porți logice cum ar fi poarta AND și poarta NOT.

Acest HS poate fi, de asemenea, proiectat folosind porți NOR unde necesită 5 porți NOR pentru construcție. Diagrama circuitului pe jumătate scăpătoare folosind porți NOR este prezentată ca:

Half Subtractor folosind Nor Gates

Tabelul Adevărului

Primul bit | Al doilea bit | Diferență (EX-OR Out) | Împrumuta (NAND Out) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Codul VHDL și Testbench

Codul VHDL pentru jumătate de scădere este explicat după cum urmează:

biblioteca IEEE

utilizați IEEE.STD_LOGIC_1164.ALL

utilizați IEEE.STD_LOGIC_ARITH.ALL

utilizați IEEE.STD_LOGIC_UNSIGNED.ALL

entitatea Half_Sub1 este

Port (a: în STD_LOGIC

b: în STD_LOGIC

HS_Diff: afară STD_LOGIC

HS_Morrow: out STD_LOGIC)

sfârșit Half_Sub1

arhitectură Comportamentul lui Half_Sub1 este

începe

HS_Diff<=a xor b

HS_Imprumutați<=(not a) and b

codul bancului de testare pentru HS este explicat după cum urmează:

BIBLIOTECA IEEE

UTILIZAȚI ieee.std_logic_1164.ALL

ENTITY HS_tb IS

END HS_tb

ARHITECTURA HS_tb OF HS_tb IS

COMPONENT SA

PORT (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

COMPONENTUL FINAL

semnalul a: std_logic: = ‘0’

semnal b: std_logic: = ‘0’

semnal HS_Diff: std_logic

semnal HS_Borrow: std_logic

ÎNCEPE

nou: HS PORT MAP (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: process

începe

la<= ‘0’

b<= ‘0’

așteptați 30 ns

la<= ‘0’

b<= ‘1’

așteptați 30 ns

la<= ‘1’

b<= ‘0’

așteptați 30 ns

la<= ‘1’

b<= ‘1’

aștepta

sfarsitul procesului

SFÂRȘIT

Subtractor complet folosind Half Subtractor

Un subtractor complet este un dispozitiv combinațional care operează funcționalitatea de scădere utilizând doi biți și este minuend și subtrahend. Circuitul consideră împrumutul ieșirii anterioare și are trei intrări cu două ieșiri. Cele trei intrări sunt minuend, subtrahend și intrările primite de la ieșirea anterioară, care este împrumutat, iar cele două ieșiri sunt diferența și împrumutul.

Diagrama logică a subtractorului complet

Tabelul adevărului pentru scăderea completă este

| Intrări | Ieșiri | |||

| X | Da | Yin | FS_Diff | FS_Imprumutați |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Cu tabelul de adevăr de mai sus, diagrama logică a diagramelor circuitelor publicitare pentru implementarea subtractorului complet folosind jumătate de substraturi este prezentată mai jos:

Subtractor complet folosind HS

Avantaje și limitări ale Half Subtractor

Avantajele jumătății subtractorului sunt:

- Implementarea și construcția acestui circuit este simplă și ușoară

- Acest circuit consumă o putere minimă în procesarea semnalului digital

- funcționalitățile de calcul pot fi realizate la viteze îmbunătățite

Limitările acestui circuit combinațional sunt:

Chiar dacă există aplicații extinse ale jumătății subtractor în multe operații și funcționalități, există puține limitări și acestea sunt:

- Circuitele cu jumătate de scădere nu vor accepta „Împrumut” din ieșirile anterioare, unde acesta este dezavantajul crucial al acestui circuit

- Deoarece multe aplicații în timp real operează pe scăderea unui număr mare de biți, dispozitivele cu jumătate de scădere nu dețin capacitatea de a scădea mulți biți

Aplicații ale Half Subtractor

Aplicațiile semicontractorului includ următoarele.

- Jumătate de scădere este utilizată pentru a reduce forța semnalelor audio sau radio

- Poate fi utilizat în amplificatoare pentru a reduce distorsiunea sunetului

- Jumătate de scădere este utilizat în ALU de procesor

- Poate fi folosit pentru a mări și micșora operatorii și, de asemenea, calculează adresele

- Jumătate de scădere este utilizată pentru scăderea celor mai puțin semnificative numere de coloane. Pentru scăderea numerelor cu mai multe cifre, poate fi utilizată pentru LSB.

Prin urmare, din teoria jumătății de deducere de mai sus, în cele din urmă, putem închide că, folosind acest circuit, putem scădea dintr-un bit binar din altul pentru a furniza ieșiri precum Diferența și Împrumutul În mod similar, putem proiecta jumătate de substractor folosind circuitul porților NAND, precum și porțile NOR. Celelalte concepte care trebuie cunoscute sunt ceea ce este cod verilog pe jumătate subtractor și cum poate fi desenată diagrama RTL?